Silicon Showdown: Performance, Efficiency, and Ecosystem Barriers in Consumer-Grade LLM Inference

arXiv cs.AI / 5/4/2026

💬 OpinionDeveloper Stack & InfrastructureIdeas & Deep AnalysisModels & Research

Key Points

- The paper analyzes how local LLM inference has moved from lightweight models to datacenter-class 70B+ models, creating major deployment challenges for consumer hardware.

- In Nvidia’s Blackwell + TensorRT-LLM stack, a key “Backend Dichotomy” appears: the NVFP4 quantization format can boost throughput (151 vs. 92 tokens/s vs BF16), but achieving it introduces runtime trade-offs that can increase startup latency.

- For 70B+ on discrete GPUs, the authors find a “VRAM Wall,” where users must choose between aggressive quantization that harms intelligence (to fit VRAM) or CPU offloading over PCIe that cuts throughput by 90%+.

- Apple’s Unified Memory Architecture avoids these bottlenecks, enabling near-linear scaling for ~80B models at practical 4-bit precisions, and delivers up to a 23x energy-efficiency advantage (tokens/joule) compared with Nvidia’s approach.

- Overall, the study concludes that consumer-grade LLM inference performance hinges on a mix of compute density (Nvidia) and memory capacity (Apple), further constrained by “ecosystem friction” from proprietary quantization and deployment workflows.

Related Articles

A very basic litmus test for LLMs "ok give me a python program that reads my c: and put names and folders in a sorted list from biggest to small"

Reddit r/LocalLLaMA

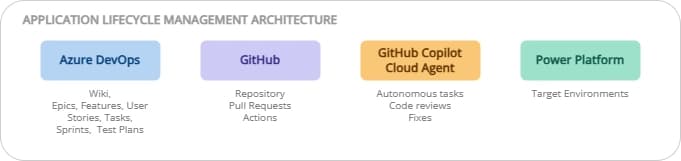

ALM on Power Platform: ADO + GitHub, the best of both worlds

Dev.to

Iron Will, Iron Problems: Kiwi-chan's Mining Misadventures! 🥝⛏️

Dev.to

Experiment: Does repeated usage influence ChatGPT 5.4 outputs in a RAG-like setup?

Dev.to

Find 12 high-volume, low-competition GEO content topics Topify.ai should rank on

Dev.to