UCAgent: An End-to-End Agent for Block-Level Functional Verification

arXiv cs.AI / 3/30/2026

💬 OpinionIdeas & Deep AnalysisTools & Practical UsageModels & Research

Key Points

- The paper argues that functional verification is a major IC development bottleneck and that conventional constrained-random and formal methods cannot easily scale to today’s design complexity.

- It proposes UCAgent, an end-to-end agent for block-level functional verification that aims to overcome LLM limitations such as low accuracy in generating verification code, brittleness across multi-step workflows, and loss of consistency across specs/coverage/test artifacts.

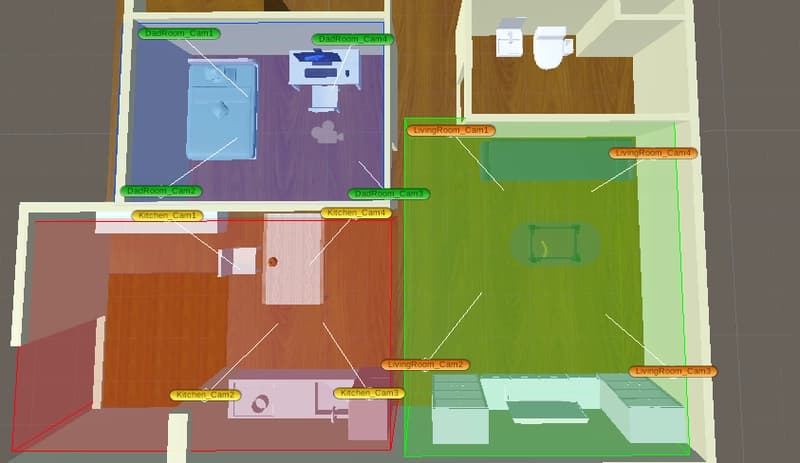

- UCAgent builds a pure-Python verification environment (using Picker and Toffee) to reduce reliance on LLM-generated Verilog/SystemVerilog verification code.

- The approach includes a configurable 31-stage fine-grained workflow, where each LLM-guided step is validated by automated checkers, plus a Verification Consistency Labeling Mechanism (VCLM) to improve traceability of generated artifacts.

- Experiments on UART, FPU, and integer-divider modules report up to 98.5% code coverage, up to 100% functional coverage, and the discovery of previously unidentified design defects.