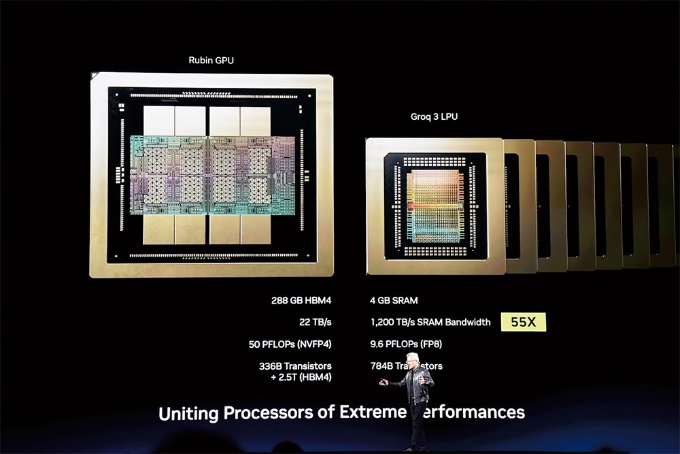

米エヌビディアは2026年3月16~19日(米国時間)に米カリフォルニア州サンノゼで開催した年次開発者会議「GTC 2026」で、推論特化チップ「NVIDIA Groq 3 LPU」を発表した。米AI(人工知能)半導体スタートアップのグロックの技術を用いて開発した。エヌビディアの主力製品であるGPU(画像処理半導体)とは異なる特徴を持つチップを製品化し、「GPU一本足」という弱点の克服を狙う。

エヌビディアはGroq 3 LPUをラック形式の「NVIDIA Groq 3 LPX」として顧客に提供する。ラック全体で256個のGroq 3 LPUを搭載した推論特化サーバーだ。エヌビディアによれば、最新のGPUとCPU(中央演算処理装置)である「Vera Rubin」世代のラックサーバー「Vera Rubin NVL72」との併用を想定している。

互いの長所を生かすことで、Vera Rubin NVL72とGroq 3 LPXを併用すると、現行のBlackwell世代の「GB200 NVL72」と比較してメガワット当たりの推論スループットが35倍、1兆パラメーターのAIモデルを稼働させた場合の費用対効果は10倍になるという。

実質買収で弱みを克服

エヌビディアは2025年12月、グロックのジョナサン・ロスCEO(最高経営責任者)ら幹部を引き抜き、かつグロックから技術ライセンス供与を受ける契約を結んだ。米CNBCは対価を200億ドル(当時のレートで約3兆1000億円)と報じており、「実質的な買収」との指摘もある。今回、発表したGroq 3 LPUはエヌビディアとグロックが共同設計した。

Groq 3 LPUは「データフロー型アーキテクチャー」のチップで、引数となるデータがそろった命令から順次実行し、プロセッサー内部でベルトコンベヤーの上を流れるように処理が進む。既存のプロセッサーの多くが採用するノイマン型アーキテクチャーと異なり、メモリーとプロセッサー間の伝送速度がボトルネックになりにくい。

LPU1個当たり500メガバイトのSRAMをオンチップで搭載し、外部メモリーへのアクセスはGPUと比較して大幅に少ない。この構造によって、電力効率に優れ超低遅延の推論処理を実現できる。

GTCの基調講演で、エヌビディアのジェンスン・ファンCEOは、Groq 3 LPXとVera Rubin NVL72を適材適所で併用する具体的な仕組みを解説した。

LLM(大規模言語モデル)の推論には「Prefill(プリフィル)」と「Decode(デコード)」という2つのフェーズがある。Prefillは入力テキストを読み込んで理解する段階で、膨大な計算量が必要になる。Decodeは順序立ててテキストなどを生成する段階で、前のテキスト情報をキャッシュしながらデータを速く動かす性能が必要になる。

計算量が必要なPrefillと文脈把握や記憶保持などのDecodeの一部をGPUで処理しつつ、テキストの生成処理をLPUが担うことで、お互いの長所を生かせるという。ファンCEOは「両極端なプロセッサーの統合で価値が高まる」と主張した。

次のページ

OpenClawを企業でも使いやすくこの記事は有料会員限定です