Abstract

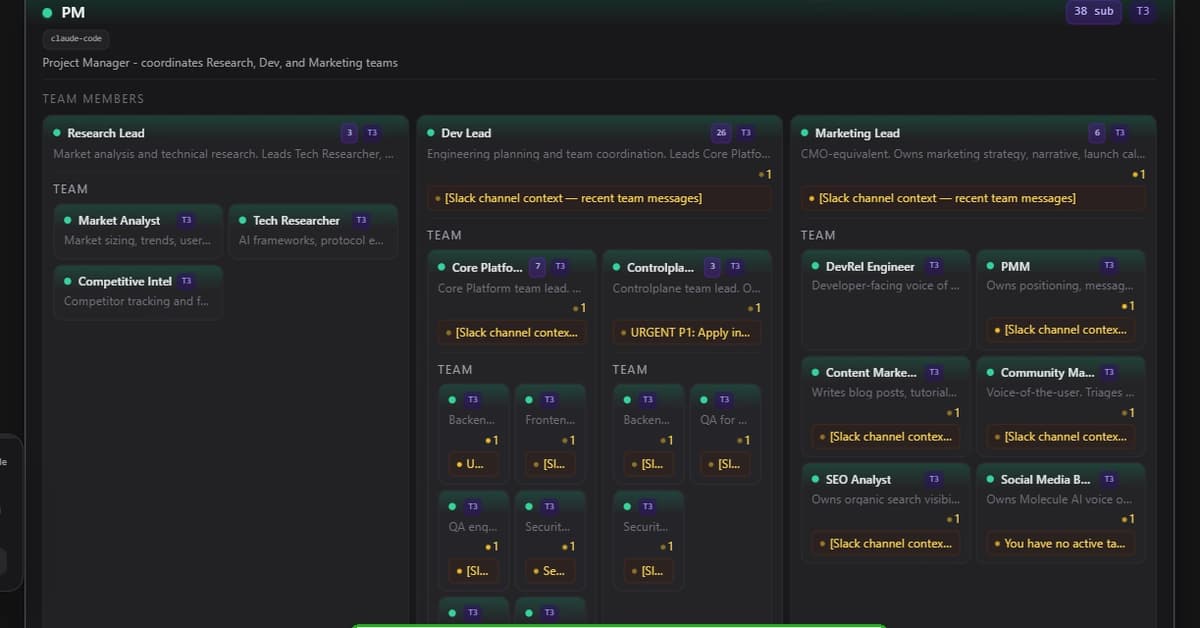

大規模言語モデル(LLM)のエッジ展開は、軽量なLoRAアダプタのライブラリにますます依存するようになっている一方で、GPU/DRAMが同時に常駐できるのはごく小さなサブセットに限られます。常駐していないアダプタを介してリクエストを処理するには、その重みをストレージからページングして読み込む必要があり、計測可能な遅延が生じます。これにより、2つのタイムスケールをもつオンライン制御問題が生まれます。すなわち、遅いタイムスケールではシステムが、速いメモリに常駐しておくアダプタを選択し、一方、速いタイムスケールでは、各リクエストを、その文脈依存の有用性が事前には未知であるようなアダプタにルーティングします。これら2つの意思決定は密接に結びついています。キャッシュは探索のコストを決め、ルータは情報を与えるフィードバックを受け取るアダプタを決めるのです。本研究では、この共同のキャッシュおよびルーティング問題を、2タイムスケールの文脈付きバンディットとして定式化し、POLAR(Paging and Online Learning for Adapter Routing)を提案します。POLARは、キャッシュを意識したLinUCBルータと、エポックベースのキャッシュ制御器を組み合わせます。2つのバリアントを検討します。固定エポック版は、任意の文脈に対する最悪時の後悔(regret)保証を伴う、堅牢なベースラインを提供します。エポック倍増版であるPOLAR+は、強制探索と改善されたキャッシュ最適化を追加し、確率的な正則性およびキャッシュ可能性条件の下で、otilde{mathcal{O}}(d\sqrt{NT}+\sqrt{KT}) の劣線形後悔を達成します。ここでNはアダプタ数、Kはキャッシュサイズ、dは文脈次元、Tはホライズンです。ルーティング項は、対数因子の範囲で標準的な文脈付きバンディットのレートに一致しており、メモリ階層がルーティング学習を本質的に遅らせないことを示しています。Qwen2.5-7Bに対して15個の実データのLoRAアダプタを使用し、計測したGPUページング遅延と組み合わせた実験では、適応的なキャッシュ制御が非適応ベースラインを大幅に上回り、理論と整合的なスケーリング傾向が観察されます。