CPUBone:低い並列化能力を持つデバイス向けの効率的なビジョンバックボーン設計

arXiv cs.AI / 2026/3/30

💬 オピニオンSignals & Early TrendsIdeas & Deep AnalysisModels & Research

要点

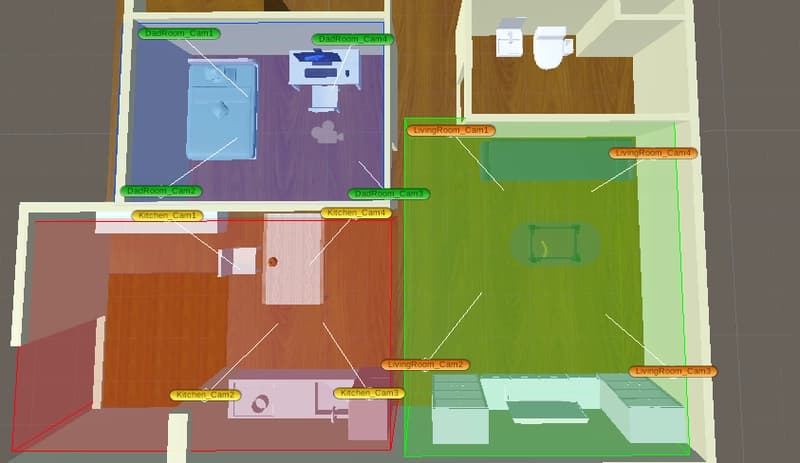

- 本論文は、ビジョンバックボーンの効率化に関する研究の多くが高並列なハードウェアを対象としている一方で、CPUベースの推論には低遅延を維持するために秒あたりの高いMAC数(MACpS)を重視した別の設計アプローチが必要だと主張する。

- 標準的な畳み込みに対する2つの修正—グループ畳み込みとより小さなカーネルサイズ—を評価し、総MAC数を大幅に削減しつつ、ハードウェア効率の維持を狙う。

- 複数のCPUデバイスでの実験を通じて、これらの畳み込みの変更は計算コストを下げても高いハードウェア効率を保てることを著者らは示している。

- CPU最適化された新しいビジョンバックボーンのファミリであるCPUBoneを提案し、さまざまなCPUハードウェアにわたって強力な速度–精度のトレードオフを達成する。

- CPUBoneの効率は、物体検出やセマンティックセグメンテーションといった下流タスクにも引き継がれることが報告されており、モデル/コードはGitHubで公開されている。