Rapidus(ラピダス、東京・千代田)の鶴崎宏亀氏(エンジニアリングセンター設計技術統括部ディレクター)は「RISC-V Day Tokyo 2026 Spring」(2026年3月5日に東京都で開催)に登壇し、同社が整備を進めているEDA(電子設計自動化)システムの最新状況を報告した(図1)。例えば、ユーザー獲得に効くAI(人工知能)エージェント志向のEDAツールのユーザーがすでに3社いるとのことだった。うち2社は国内、残り1社は海外の企業である。

同社が整備中のEDAシステムについて初めて公の場で発表したのは、2024年8月1日に東京都で行われたイベント「RISC-V Day Tokyo 2024 Summer」の講演だった。登壇者は今回と同じ鶴崎氏である。当時から、同氏は台湾TSMC(台湾積体電路製造)などの競合ファウンドリー(半導体受託生産会社)と設計サポート面で差異化するポイントとして、AI技術を使ったEDAツール「Raads」をアピールしていた。

今回の講演もRaadsが中心だったが、AIの進化に合わせて、Raadsの正式名称が変わった。以前はAIが設計を支援するという意味で、「Rapidus AI-Assisted Design Solution」の短縮形としてRaadsを使っていた。「AIの進歩は著しく、AIが設計者を支援するというよりも、AI自体が設計するようになってきた。いわゆるAIエージェントである」(鶴崎氏)。RaadsのAIエージェント化を進めており、「Rapidus AI-Agentic Design Solution」の短縮形として同じRaadsを使うようになった。

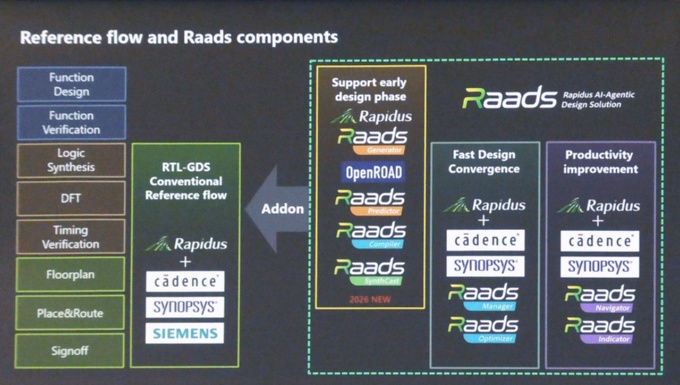

Raadsは複数のEDAツールから成る。これらは2種類に分けられる(図2)。1種類は、EDAベンダーのAI処理機能付きEDAツールにラピダスの学習済みモデルを組み合わせたものである。ユーザーが設計したSoC(System on a Chip)の論理データ「RTL(Register Transfer Level)データ」を、製造に使うGDS-II形式のマスク・レイアウト・データに変換する際に利用される。Raadsツールを併用することによって、設計期間を短縮したり、設計生産性を上げたりできる。

もう1種類は、ラピダスが独自に開発・整備したツールで3つある。いずれもSoCの上流設計(RTLデータの設計など)で使う。1つ目は、自然言語(現在、英語)からRTL設計データを生成する「Raads Generator」。2つ目は、RTL設計データからSoCの特性(消費電力、性能/速度、チップ面積:いわゆるPPA)を見積もる「Raads Predictor」。3つ目は「Raads SynthCast」で、Raads GeneratorとRaads Predictorを統合したものである。

次のページ

新規参入ファウンドリーの不利益を補うこの記事は有料会員限定です